|

|||||||

|

Информация о работе с процессором SWX03S, используемом в Yamaha PSR-E473

Время создания: 03.04.2025 10:53

Текстовые метки: yamaha, E473, синтезатор, процессор, микропроцессор, контроллер, SH-2, RISC, SuperH

Раздел: Музыка - Пианино - Yamaha

Запись: xintrea/mytetra_syncro/master/base/1743666781f8ucvka74a/text.html на raw.githubusercontent.com

|

|||||||

|

|

|||||||

|

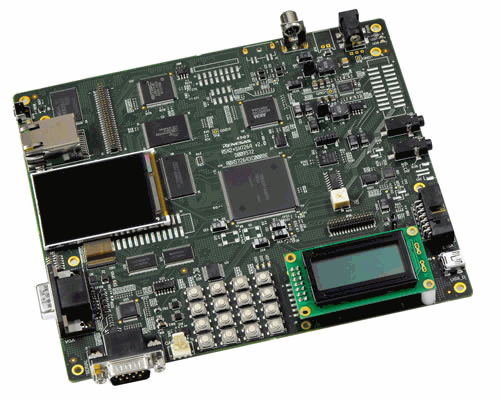

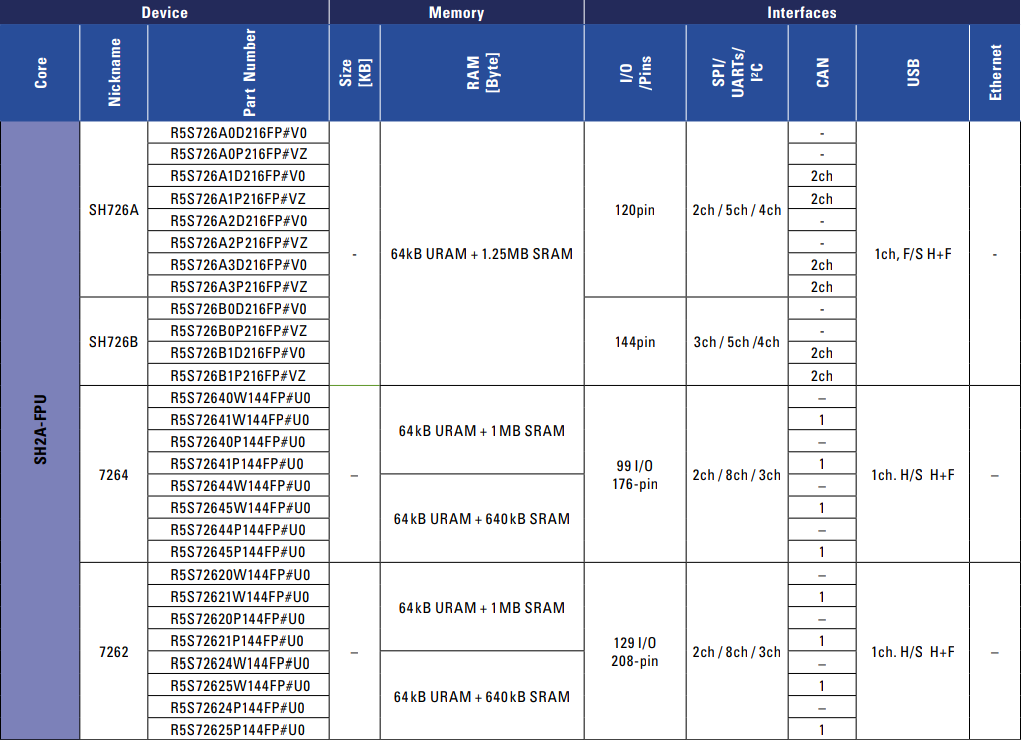

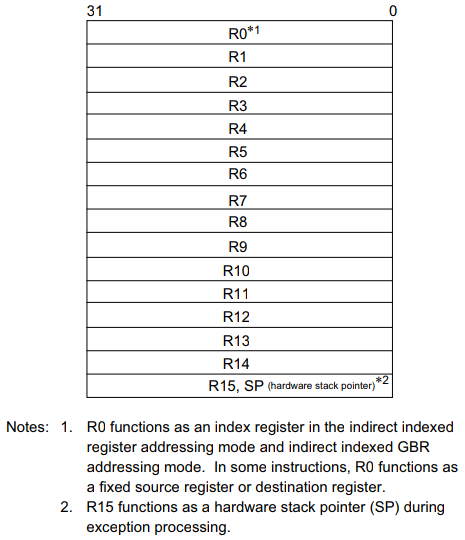

В синтезаторе Yamaha E-473 используется микропроцессор SWX03S. Обозначение в документации Yamaha - SCC105A, раrt. N: YK611A0. Внутренняя частота 135.4752MHz. Внешний тактовый генератор на 67.7376MHz. Предположительная архитектура - SuperH SH-2 RISC (Данное предположение неверно!) Что есть про этот микропроцессор в интернете? Официальная документация на SH-2 Руководство программиста SH-2 (англ. SuperH SH-2 Programming Manual): Говорят, что есть в архивах Renesas (Product Selector: RH850 Automotive MCUs, Product Selector: RX 32-Bit Performance / Efficiency MCUs). Там должны быть описаны регистры, инструкции и тайминги. По факту упоминаний архитектуры SuperH или SH-2 не найдено. Однако, по косвенным признакам, аналогичную архитектуру могут иметь чипы SH7264 или SH7262. Набор Starter Kit с чипом SH7264 выглядит так:

Документация для чипов SH7264 и SH7262 общая.

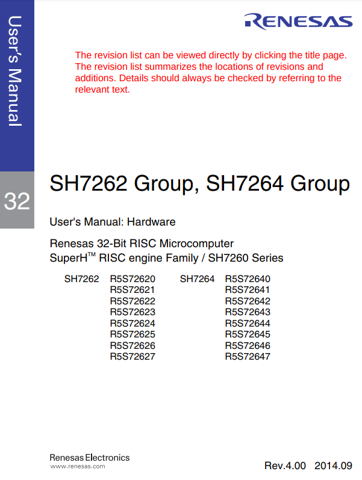

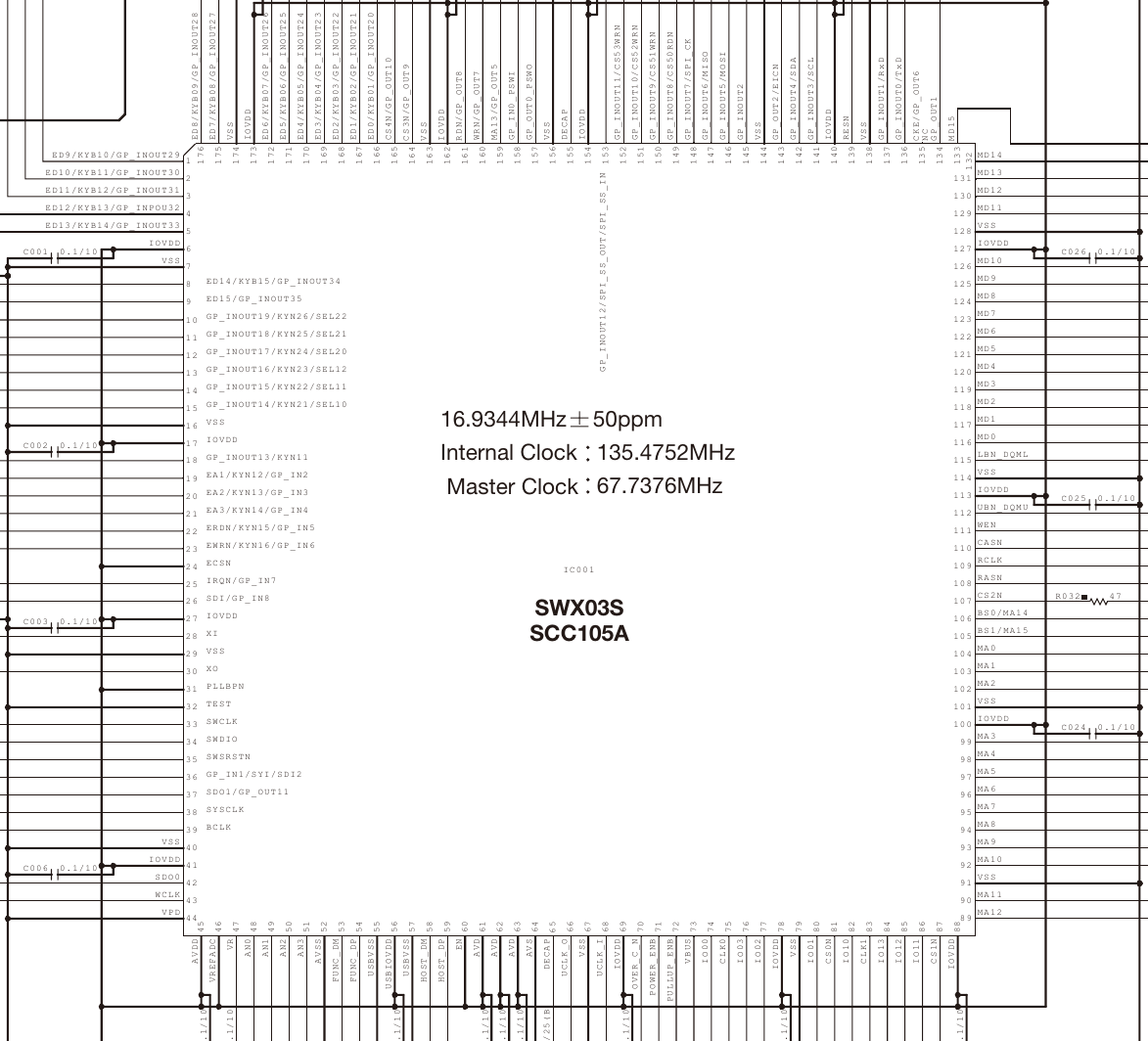

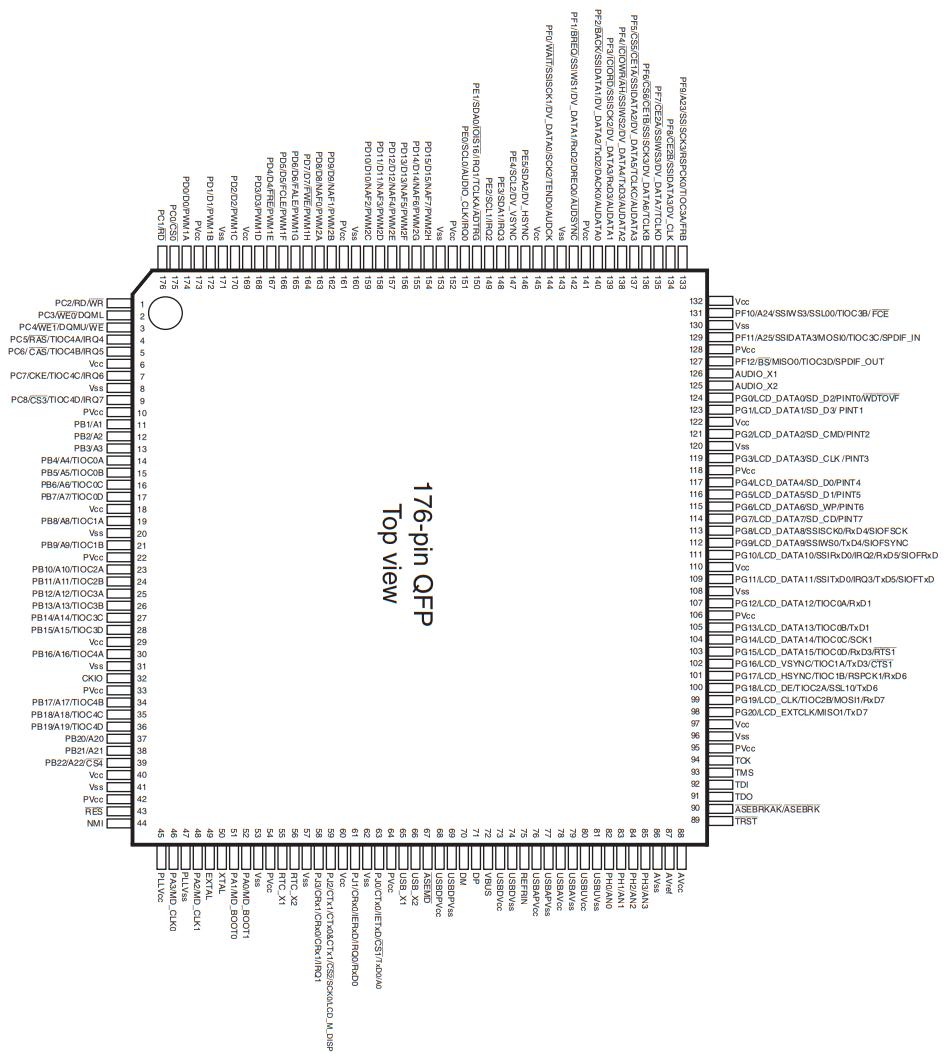

Ссылка на документацию: https://www.renesas.com/en/document/mah/sh7262-group-sh7264-group-users-manual-hardware?queryID=ae099f5a0d5a9fd664aff564a76d0027 Еще больше официальных документов вот по этой ссылке: https://www.renesas.com/en/products/microcontrollers-microprocessors/other-mcus-mpus/superh-risc-engine-family-mcus/sh7262-32-bit-microcontrollers?queryID=ae099f5a0d5a9fd664aff564a76d0027#documents Почему инженеры Yamaha могли выбрать именно этот процессор? Вот что про процессор SH-2 написано в рекламных материалах: Основные преимущества контроллеров SuperH без встроенного ПЗУ Скорость Ядро SH-2A является суперскалярным. Это означает, что оно может выполнять две команды за один такт. Оно обеспечивает производительность до 630 DMIPS. Работа с экранами Семейство контроллеров SuperH оснащено несколькими периферийными устройствами для управления TFT-экранами и поддерживается широким спектром программного обеспечения для поддержки этой функциональности. Включая встроенный SRAM объемом до 2,5 МБ. Возможность масштабирования Являясь основой платформы SuperH, семейство SHC-ROMless позволяет значительно расширить возможности за счет процессора SuperH, а также снизить стоимость и функциональность за счет контроллеров SuperH со встроенной флэш-памятью. Связь Семейство SuperH предлагает все возможности подключения, которые только можно пожелать для высокопроизводительных процессоров, включая CAN, USB и Ethernet. Семейство контроллеров SuperH без встроенного интерфейса ROM обладает всеми функциями подключения, необходимыми для широкого спектра приложений и областей применения. Интеграция Семейство контроллеров SH Romless также включает устройства со встроенной ОЗУ объемом до 2,5 МБ, что означает, что вы можете заменить внешнюю оперативную память и видеобуфер на эту внутреннюю оперативную память. Кроме того, поскольку эти устройства могут запускать код из этой внутренней оперативной памяти, внешняя флэш-память NOR может быть заменена более дешевой последовательной флэш-памятью. Это может обеспечить значительную экономию затрат на спецификацию. Так же в рекламе утверждается, что на этом процессоре работает Linux. Формально это так, но т.к. в SH-2 нет модуля MMU, то запустить можно только упрощенный μClinux, который считается устаревшим, и не является стандартным Linux-дистрибутивом. Другими словами, SH-2 (без MMU) официально не поддерживается в современных ядрах Linux. Ножки микросхем По ножкам: у SWX03S (SCC105A) имеется 176 выводов. У серии SH7262/SH7264 следующее кол-во ножек: SH7262 1Mb version - 176 ножек SH7262 640Kb version - 176 ножек SH7264 1Mb version - 208 ножек SH7264 640Kb version - 208 ножек Очень точное соответствие с SH7262! Весьма возможно, что SWX03S - это перелицованый SH7262. Теперь можно сравнить картинки с даташитов.

Это микросхема SWX03S

Это микросхема SH7262 Как видно, совпадений по ножкам нет. Совпадает только общее количество. Нужно составить таблицы для одного и второго чипа, и попытаться найти соответствия. Если сигналы просто перекоммутированы на другие выводы, это можно заметить. Надо разбираться дальше. Согласно даташиту на SH7262, его ножки могут выполнять 4 функции. И таблица обозначения ножек содержит 4 столбца. Надо разбираться, что значат эти функции. Проверено: SH7262 не может быть чипом Yamaha. В SWX03S используется архитектура ARMhf а не SH. Ошибки в официальной документации В документе User's Manual: Hardware Renesas 32-Bit RISC Microcomputer SuperH RISC engine Family / SH7260 Series, файл REN_r01uh0134ej0400_sh7262_MAH_20140926.pdf (ссылка на него дана выше) на стр. 11 раздела 1, написано следующее: SH7262 176-pin QFP, 24-mm square, 0.5-mm pitch JEITA package code: P-LQFP176-24 x 24-0.50 Renesas code: PLQP0176KB-A SH7264 208-pin QFP, 28-mm square, 0.5-mm pitch JEITA package code: P-LQFP208-28 x 28-0.50 Renesas code: PLQP0208KB-A Т. е. у SH7262 имеется 176 ножек, а у SH7264 - 208. В то же время в соседнем документе SuperH platform brochure 32-bit RISC Microcontrollers (файл REN_R01CL0014ED0200_FLY_20121015.pdf), в котором даются рекомендации выбора процессора, имеется таблица:

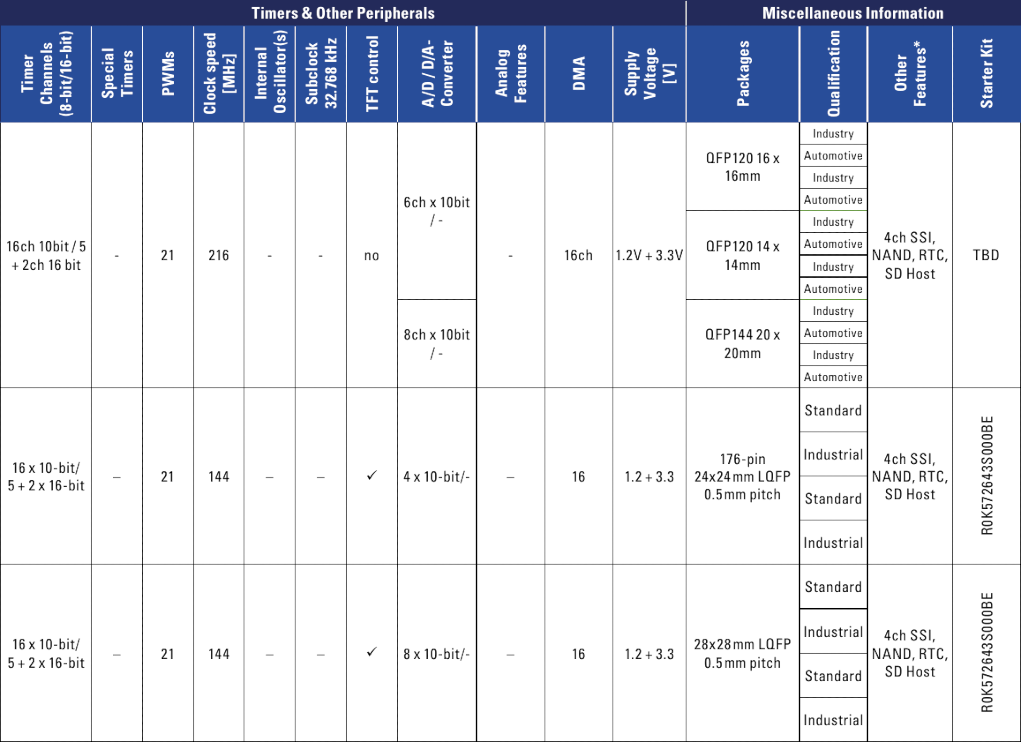

И здесь уже наоборот: для 7262 указано 208 ножек, а для 7264 - 176 ножек. Непонятно кому верить. Характеристики процессора В любом случае, теперь становится ясно, что в SH7262/7264 используется ядро архитектуры SH2A со встроенным сопроцессором для работы с плавающей точкой (FPU). SH2A - это 32-х битный процессор. Имеет на борту ОЗУ в 640K (SRAM) + 64K (high speed) или 1Mb (SRAM) + 64K (high speed), но не имеет ПЗУ, и для хранения исполняемого кода пользуется внешней Flash-памятью. Есть встроенный кеш на 16К. Процессор поддерживает 112 базовых инструкций. Количество прерываний: 17 ( NMI, IRQx8, PINTx8 ) Watchdog timer: 1 Clock Sync/Clock Async: 8 16-ти битовые таймеры: 7 (MTU2 x 5, CMT x 2) CPU SH-2A/SH2A-FPU Features • Original Renesas Technology architecture • 32-bit internal data bus • General-register architecture - 17 32-bit general registers - 4 32-bit control registers - 4 32-bit system registers - Register banks for fast interrupt response • RISC-type instruction set (upward-compatible with SH Series) - Instruction length: 16-bit basic instructions for improved efficiency, and 32-bit instructions for improved performance and ease of use - Load-store architecture - Delayed branch instructions - Instruction set based on C language • Superscalar architecture allowing simultaneous execution of two instructions, including FPU • Instruction execution time: Max. 2 instructions/cycle • Address space: 4 Gbytes • On-chip multiplier • Five-stage pipeline • Harvard architecture Порядок чтения байт: Big Endian (Некоторые версии SH-2A (например, SH7205) поддерживают динамическое переключение между Big и Little Endian через регистр MMUCR (Memory Management Unit Control Register), однако по умолчанию после сброса процессор всегда стартует в Big Endian). Надо проверить возможность переключения BE/LE в документации на SH7262, так как порядок в дампах больше всего похож на LE, а MMU в SH7262 нет, а значит и переключение на BE/LE невозможно? На самом деле работа и в BE и в LE возможна! Переключение происходит через специальный управляющий регистр. Регистры:

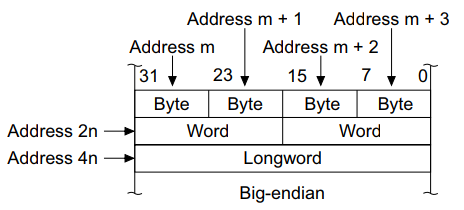

Формат работы с данными в SH-чипе Используются форматы данных: byte, word и longword. Доступ к памяти может осуществляться как к 8-bit bytes, 16-bit words или 32-bit longwords. Если операнд в памяти имеет длинну менее 32 бит, он будет помещаться в регистр (при чтении?) в sign-extended форме или zero-extended форме. К операнду размером word следует обращаться, начиная с границы слова (2-байтовый четный адрес: address 2n), а к операнду longword - с границы длинного слова (4-байтовый четный адрес: address 4n). Если это правило не соблюдается, возникает ошибка адреса. Доступ к байтовому (byte) операнду можно получить с любого адреса. Далее написано буквально следующее: "Only big-endian byte order can be selected for the data format". Что означает - для формата данных можно выбрать только порядок байтов Big-Endian.

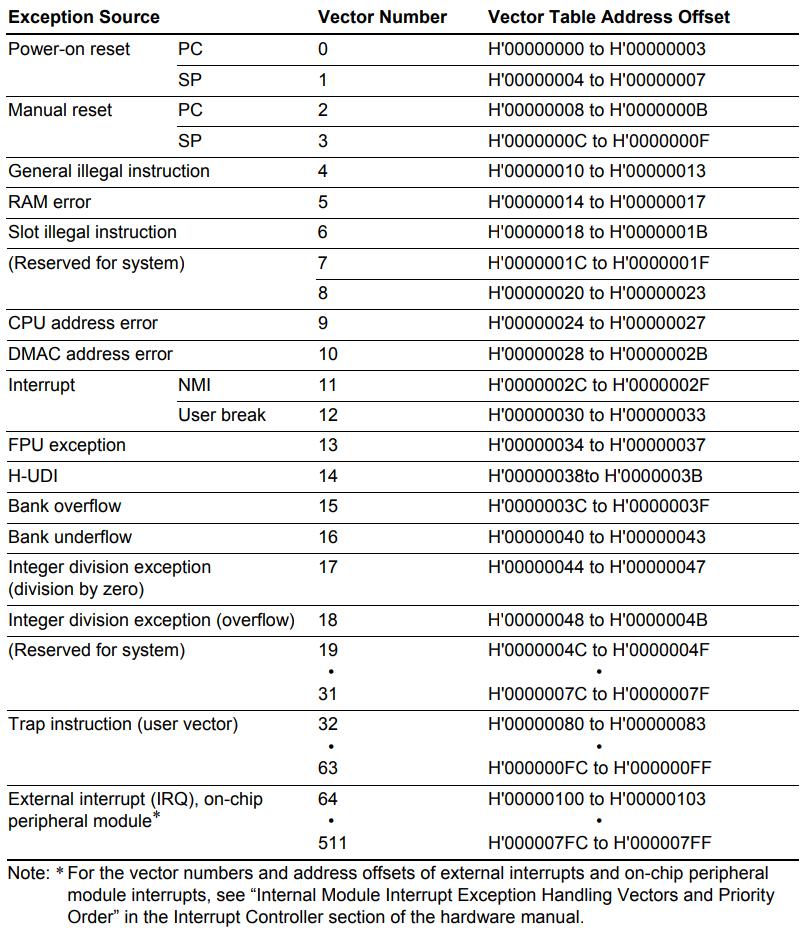

Формат непосредственных данных, размещаемых в коде инструкции Непосредственные данные размером в байт находятся в коде команды. Непосредственные данные, к которым обращаются команды MOV, ADD и CMP/EQ, расширяются по знаку и обрабатываются в регистрах как данные longword. Непосредственные данные, к которым обращаются команды TST, AND, OR и XOR, расширяются нулями и обрабатываются как данные longword. Таким образом, команды AND с непосредственными данными размером в байт, всегда очищают верхние 24 бита регистра назначения. В коде 32-разрядной инструкции MOVI20 или MOVI20S могут храниться 20-разрядные непосредственные данные. Инструкция MOVI20 сохраняет непосредственные данные в регистре назначения в форме sign-extention. Инструкция MOVI20S сдвигает непосредственные данные на 8 бит в верхнем направлении и сохраняет их в регистре назначения в форме sign-extention. Непосредственные данные размером word или longword не могут находиться в коде команды, а хранятся в памяти. Доступ к памяти осуществляется с помощью команды передачи данных (MOV), использующей относительную адресацию через регистр PC со смещением. Инициализация регистров PC и SP Начальные значения программного счетчика PC (program counter) и указателя стека SP (stack pointer) берутся из таблицы векторов прерываний. Используются адреса, прописанные в ячейках 0x00000000 (PC) и 0x00000004 (SP) в случае сброса через выключение питания, и адреса в ячейках 0x00000008 и 0x0000000C при ручном сбросе. Затем регистр векторной базы (vector base register, VBR) сбрасывается на 0x00000000, биты маски прерываний (от I3 до I0) в регистре состояния (SR) устанавливаются на 0xF (1111), а биты BO и CS инициализируются равным 0. Бит BN в IBNR из INTC также инициализируется равным 0. Кроме того, в продуктах с FPU, FPSCR инициализируется значением 0x00040001. Выполнение программы начинается с адреса PC, полученного из таблицы векторов прерываний. Таблица векторов прерываний Таблица векторов прерываний располагается по адресам 0x00000000 - 0x000007FF.

Открытые проекты и эмуляторы для разбора машинного кода GNU Binutils (GAS, objdump): — Поддерживает ассемблер и дизассемблирование SH-2. — Исходный код в репозиториях GCC (GitHub). (см. ниже про sh-elf) Эмулятор MAME: — Реализует SH-2 для аркадных автоматов (например, Sega Saturn). — Код CPU-ядра: mame/src/devices/cpu/sh/sh2.cpp. Проект QEMU: — Частичная эмуляция SH-2 (менее точная, чем MAME). Если нужно дизассемблировать код Могут помочь утилиты пакета sh-elf-*: Имеется утилита sh-elf-objdump (из пакета GNU Tools for SuperH). Где sh - это не сокращение от shell, а название архитектуры. Взять его можно с https://github.com/andwn/sh-gcc-toolchain. Этот проект представляет собой просто один Makefile. При его сборке командой make, выкачиваются различные архивы с каких-то зеркал, на которых лежат исходники для Hitachi SuperH-2. После сборки, файлы устанавливаются либо традиционной командой sudo make install, либо через checkinstall -D (для Debian-подобных дистрибутивов). Чтобы установка через checkinstall -D нормально сработала, перед запуском команды надо создать каталог /opt/toolchains, такая особенность заложена в Makefile. А так же при запуске checkinstall -D необходимо изменить номер версии Version (пункт 3) со строки toolchain на что-нибудь типа 1.0.0, иначе пакет не будет создан. После этого, становится доступна программа sh-elf-objdump. Она находится в каталоге /opt/toolchains/sh-elf/bin. Его надо прописать в переменную PATH. Так как все исполнимые файлы в этом каталоге начинаются на "sh-elf-*", они не будут перекрывать никакие другие системные инструменты. Пример запуска: sh-elf-objdump -D -b binary -m sh2 firmware.bin Какие архитектуры будут доступны sh-elf-objdump --help: sh-elf-objdump: поддерживаемые цели: elf32-sh elf32-shl coff-sh coff-shl coff-sh-small coff-shl-small elf32-little elf32-big srec symbolsrec verilog tekhex binary ihex plugin sh-elf-objdump: поддерживаемые архитектуры: sh sh2 sh2e sh-dsp sh3 sh3-nommu sh3-dsp sh3e sh4 sh4a sh4al-dsp sh4-nofpu sh4-nommu-nofpu sh4a-nofpu sh2a sh2a-nofpu sh2a-nofpu-or-sh4-nommu-nofpu sh2a-nofpu-or-sh3-nommu sh2a-or-sh4 sh2a-or-sh3e Так же могут помочь интерактивные дизассемблеры: — Radare2/Ghidra с поддержкой SH-2. В Ghidra v. 11.3.1 точно есть поддержка архитектур SuperH и SuperH4. Поэтому непонятно, входит ли SH-2 в архитектуры SuperH и SuperH4. Похоже, все-таки SH-2 должна поддерживаться, ибо в каталоге /opt/ghidra_11.3.1_PUBLIC/Ghidra/Processors/SuperH/data/languages лежат файлы: sh-1.sla sh-1.slaspec sh-2a.sla sh-2a.slaspec sh-2.sla sh-2.slaspec superh2a.cspec superh.cspec superh.ldefs superh.pspec superh.sinc |

|||||||

|

Так же в этом разделе:

|

|||||||

|

|||||||

|

|||||||

|