|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

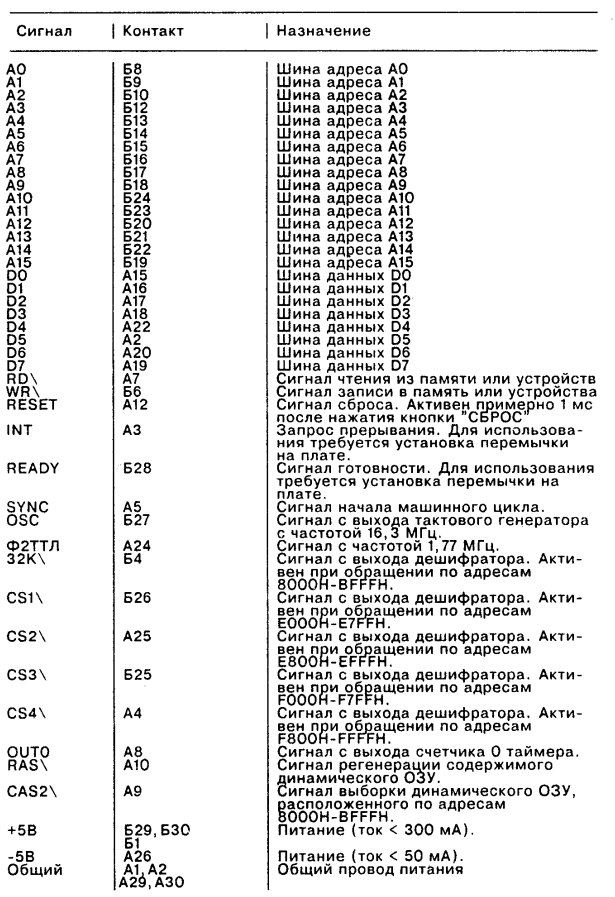

Сигналы, выведенные на разъем "Внутренний интерфейс" ПЭВМ "Микроша"

Время создания: 06.11.2021 18:48

Текстовые метки: Микроша, разъем, интерфейс, внутренний, сигнал, распиновка, расключение, контакт, шина, адресс, данные

Раздел: Компьютер - Микроша

Запись: xintrea/mytetra_syncro/master/base/1636213730hs01f6tkje/text.html на raw.githubusercontent.com

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Согласно схеме, на разъеме "Внутренний интерфейс" присутствуют следующие сигналы шины адреса (ША) и шины данных (ШД):

Так же выведены следующие управляющие сигналы: Обозн. Конт. Описание /RD А-7 Сигнал чтения, выход MEMR (ножка 4) контроллера ПДП DD2 К580ВТ57 (сигнал проходит через логическую схему DD6.1) /WR Б-6 Сигнал записи, выход микропроцессора WR (ножка 18). МП: Выход сигнала управления записью в память или во внешнее устройство. Низкий активный уровень сигнала указывает на то, что микропроцессор выдал данные на ШД OUT0 А-8 Выход канала 0 (ножка 10) микросхемы таймера DD22 К580ВИ53 INT А-3 Возможно не расключен, возможно приходит на вход 14 (INT, запрос прерывания) микропроцессора К580ВМ80А CAS2 А-9 Разряд E2 с выхода 11 дешифратора DD17 К155ИД4 RES А-12 Сигнал RESET с выхода 1 микросхемы DD1 К580ГФ24 МП: Вход сигнала начальной установки процессора. После окончания сигнала (длительность должна быть не менее трех периодов синхросигнала) прогаммный счетчик устанавливается в нуливое состояние и МП начинает выполнять программу с нуливого адреса F2T А-24 Сигнал Ф2TTL с выхода 6 микросхемы DD1 К580ГФ24 (ТТЛ тактовый выход второй фазы) RDY Б-28 Сигнал READY с выхода 4 микросхемы DD1 К580ГФ24 - неправльно. Правильно: контакт не расключен. Является пином 2 перемычки 1-2-3. Возможно, для отладки схемы, временно должен подключаться к ноге 3 DD1 К580ГФ24 (вход READY)

OCS Б-27 Тактовые сигналы опорной частоты (ТТЛ) с выхода 12 микросхемы DD1 К580ГФ24 /32К Б-4 Сигнал выбора "32К", для интервала 8000-BFFF /CS1 Б-26 Сигнал выбора интервала E000-E7FF /CS2 А-25 Сигнал выбора интервала E800-EFFF /CS3 Б-25 Сигнал выбора интервала F000-F7FF /CS4 А-4 Недокументирован, возможно сигнал выбора диапазона ROM-памяти F800-FFFF SYNC А-5 Сигнал синхронизации SYNC с выхода 19 микропроцессора DD5 К580ВМ80А. МП: Выход сигнала синхронизации, определяющего начало каждого машинного цикла команды. Используется для идентификации действий, выполненных в микропроцессоре, и синхронизации поциклового управления процессором Сигналы, начинающиеся со слеша "/", по всей видимости, являются инверсными (true - это низкий уровень сигнала). Так же на разъеме "Внутренний интерфейс" присутствуют питающие контакты:

Физическое размещение контактов на разъеме:

Сторона А - это дальний от пользователя ряд контактов в разъеме "Внутренний интерфейс", когда пользователь сидит за компьютером. Сторона Б - это ближний к пользователю ряд контактов. Так же есть таблица распиновки разъема "Внутренний интерфейс", взятая из книги автора Микроши С. Н. Попова "Персональный компьютер Микроша и его программное обеспечение".

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Так же в этом разделе:

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

на данн

на данн